Uživatelské nástroje

Postranní lišta

pripravky:fpga:zybo:start

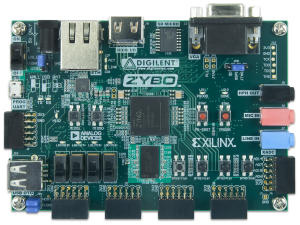

ZYBO

Documentation

Reference designs

Description

- FPGA

- Xilinx Zynq-7000 (XC7Z010-1CLG400C), Zynq Datasheet Xilinx Zynq

- 28,000 logic cells

- 240 KB Block RAM

- 80 DSP slices

- On-chip dual channel, 12-bit, 1 MSPS analog-to-digital converter (XADC)

- 650 MHz dual-core Cortex™-A9 processor

- Peripheral devices

- On-board JTAG programming and UART to USB converter

- DDR3 memory controller with 8 DMA channels

- 512 MB x32 DDR3 w/ 1050Mbps bandwidth

- 128 Mb Serial Flash w/ QSPI interface

- microSD slot (supports Linux file system)

- High-bandwith peripheral controllers: 1G Ethernet, USB 2.0, SDIO

- Low-bandwidth peripheral controller: SPI, UART, I2C

- Dual-role (Source/Sink) HDMI port

- 16-bits per pixel VGA output port

- Trimode (1Gbit/100Mbit/10Mbit) Ethernet PHY

- OTG USB 2.0 PHY (supports host and device)

- External EEPROM (programmed with 48-bit globally unique EUI-48/64™ compatible identifier)

- Audio codec with headphone out, microphone and line in jacks

- 6 pushbuttons, 4 slide switches, 5 LEDs

- Six Pmod ports (1 processor-dedicated, 1 dual analog/digital)

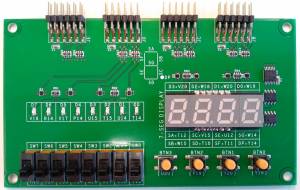

I/O Expansion Board for ZYBO

Number of items: 62

Every Board Contains:

- 8x LED

- 8x Switch

- 4x Button

- 4 Position 7-Segment Display

All I/O are active in logic '1' including display. Schema of revision 1.2.

/var/www/app/current/data/pages/pripravky/fpga/zybo/start.txt · Poslední úprava: 3. 11. 2018 20:13:45 CET autor: novotnym