Uživatelské nástroje

Postranní lišta

pripravky:fpga:dpacard:start

Obsah

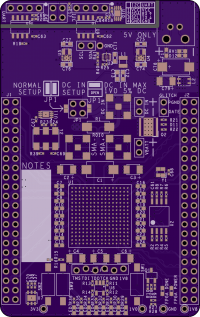

DPA Card Development Board Rev3.0

Description

- FPGA: XC7A35T-FTG256-2I - Industrial -40°C ~ 85°C

- SPI FLASH: N25Q128 (SPI x4, 128 Mb, 1.8V)

- 100 MHz 10 ppm fixed oscillator

- Si514 (514CBB000112AAG) CMOS tunable oscillator (I2C)

- Vcore IC: MP8843 (5mV step) (I2C)

- SHA-256 EEPROM (DS28E15)

- TRNG, ECDH, ECDSA, SHA-256 EEPROM (ATECC508A) (I2C)

- Glitch insertion on Vcore rail (PD54003L-E @ 500MHz)

- Most of configuration can be done via I2C or JTAG

- 64kb EEPROM for storing configration data (I2C)

- SMAs for a differential probe (SCA)

- Dedicated SMA for Vcore (SCA)

Documentation

- Board schematic : schema_rev3_0.pdf

- OrCAD board file: artix7-dpa_rev3_0.zip

- GERBER files: artix7-dpa_rev3_0_gerber.zip

- Assembly diagrams: artix7-dpa_rev3_0_asm.pdf

- BOM: bom_rev3_0.zip

Reference Designs

- The test design with a LED counter, UART loopback and all I/O pins are generating a 5 MHz square wave. dpa_test_rev3_0.zip

Improvements related previous board revision

- Complete redesing of the power supply (improved filtering), decreased voltage step for the Vcore from 10 mV to 5mV, added support for L and LI speedgrades with lower default Vcore than 1.0 V

- Price and assembly complexity has been lowered (the profi assembly company is no more required).

- Components have been renumbered for better identification in BOM, the documentation is more straithforward

- All components with a same value have unified packages, 0402 is the default footprint for all discrete components

- Components with EOL and NRND status have been replaced

Known issues and problems

- Stencil openings for MP8843 and XCL214 ICs are poor - they have to be wider a little bit.

- 1V8 and 3V3 are enabled by POWER GOOD signal of MP8843 - could case a problem in case of the direct Vcore via dedicated SMA.

Unperformed tests

Power OKFPGA via JTAG livesLEDs and buttonsUART loop backI/O pinsI2C chain discoveryWorking on FPGA side only, the ISO1540 is shorted again (Replace with SI8600A).Tuning the MP8843 via I2C- Tuning the oscillator via I2C

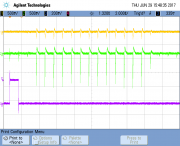

LNA Test

- Using BGA2869 IC, any LNA with the same footprint (SOT-363) can be used

- Tested by Honza Říha, observations: every piece has different behavior (different gain), but the best piece is comparable/better than the original LNA.

- Tested by Matěj Bartík, observations: a new batch of 3 PCB assembled in our infrared oven, all LNAs have same properties → they can't be soldered by hand.

Would we like to have an LNA onboard on DPACard?

DPA Card Development Board Rev2.1 (with RF transistor)

Description

- FPGA: XC7A35T-FTG256-2I - Industrial -40°C ~ 85°C

- SPI FLASH: N25Q128 (SPI x4, 128 Mb, 1.8V)

- 100 MHz 10 ppm fixed oscillator

- Si514 (514CBB000112AAG) CMOS tunable oscillator (I2C)

- TPS62360ZHT (10mV step) (I2C)

- SHA-256 EEPROM (DS28E15)

- TRNG, ECDH, ECDSA, SHA-256 EEPROM (ATECC508A) (I2C)

- Glitch insertion on Vcore rail (PD54003L-E @ 500MHz)

- Most of configuration can be done via I2C or JTAG

- 64kb EEPROM for storing configration data (I2C)

- SMAs for a differential probe (SCA)

- Dedicated SMA for Vcore (SCA)

Documentation

- Schematic: schema_dpacard_2_1.pdf.

- Complete documentation pack: DPACard_rev2.1.zip

Reference Designs

- Same as Rev1 design, but there is the need to change FPGA clock pin.

Improvements related previous board revision

- FT2232H USB<>UART/I2C has been removed, it's easier to connect the board to a Rapsberry Pi and managed it over SSH.

- Si514 tunable oscillator is finally assembled (digikey stocked)

- Pitch between SMA connectors has been increased

- Support for powering FPGA core via SMA or pin header has been added

- RF (@500MHz) transistor (PD54003L-E) has been added as Vcore glitch support

- No more manual soldering for bitstream AES encryption key battery - universal circuit with a pin header

- ATECC508A (I2C) has been added.

- EEPROM for identification/configuration data has been added.

- Optional pin header for interconnecting I2C bus with the FPGA

- Button are industry grade

- A large (1000uF) bulk capacitor has been added.

Zjištěné problémy

- Neproběhla další diskuze k vývoji (zatím jsem nedostal žádnou zpětnou vazbu k DPA nebo PUF)

- Je potřeba kouknout na RF tranzistor a zjistit jeho vhodnost pro glitch insertion (alespoň teoreticky)

- Není otestováno, zda optočleny při zapojení stále zkratovávají 3V3 zdroj.

Vývojová deska DPA Card rev1.0

Description

- FPGA: XC7A35T-FTG256-1C (0-85°C)

- SPI FLASH: N25Q032A11ESE40G (SPI x4, 32 Mb, 1.8V)

- 100 MHz 10 ppm oscilátor

- Vcore IC: TPS62360ZHT (10mV step)

- SHA-256 EEPROM (DS28E15)

Documentation

- Schéma celé desky: FPGA část a Napájení a komunikační část.

Reference Designs

- Vzorový design s čítačem pro Vivado 2016.1 dpa_test.zip.

Zjištěné problémy

- Nefunguje převodník USB <> UART, I2C (FTDI FT2232H)

- Při zapojených optočlenech jde 3V3 zdroj do zkratu

- SMA konektory jsou příliš blízko u sebe, jde připojit pouze jeden koaxiální kabel (naštěstí to stačí)

- Napájecí konektor výrazně přesahuje desku

- Pájecí maska není rozdělená pro lepší izolaci

- Hodinový signál připojen na nevhodný pin (změna označení oproti Spartan-6 nebo -3E)

Literatura

/var/www/app/current/data/pages/pripravky/fpga/dpacard/start.txt · Poslední úprava: 3. 12. 2017 12:42:29 CET autor: bartimat