Uživatelské nástroje

Postranní lišta

pripravky:fpga:step4puf:start

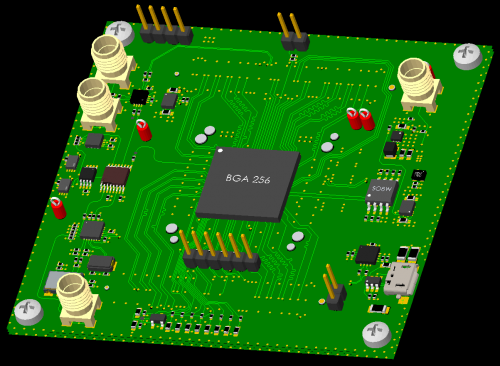

Scalable Test & Evaluation Platform 4 Physically Unclonable Function

Návrh univerzální architektury pro měření.

Plánovaná podpora Xilinx:

- Artix 7

- Spartan 6

- Spartan 3/3A

- Kintex UltraScale(+)

Pro začátek můžeme podporovat všechno co má FT(G)256 pinout, od Spartan-2, Virtex-2, Altera Cyclone II - VI, Altera MAX.

Dražší čipy používat bez socketu, protože cena FPGA převyšuje cenu desky.

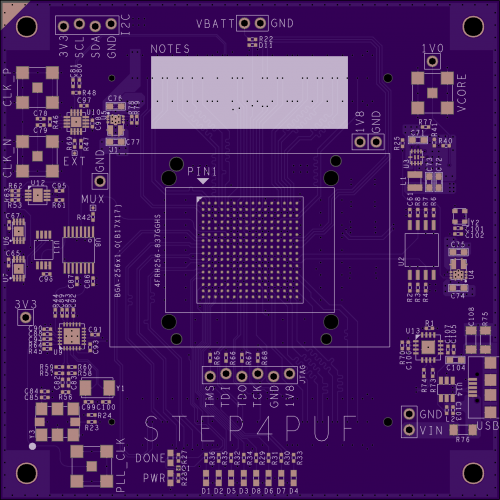

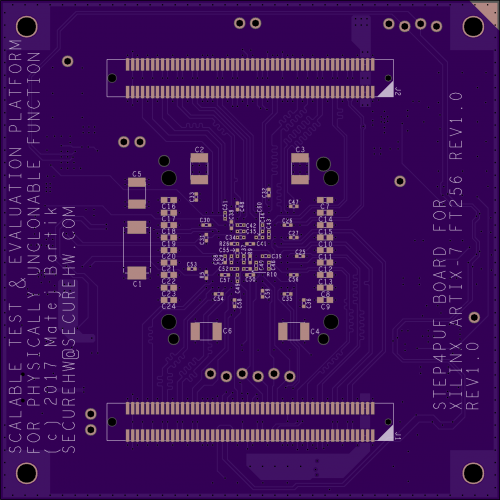

Artix-7 Rev1.0

- Odhadovaná cena 400€, jedno FPGA stojí 40€ na farnellu

- Podpora pro čínský i US socket

- 4x RGMII interface, 20xLVCMOS18 GPIO, 4xLVCMOS33 pro UART a I2C

- 3x externí hodinový signál

- Speciální „clock processing“ část s PLL (s destabilizační funkcí), laditelné i fixní oscilátory

- 8x LED

- USB-UART převodník, možnost napájet celou desku z USB

Dokumentace a výrobní data

Obrázky

Zjištěné chyby

- Pravý horní montážní pin socketu má špatné umístění

- Socket má dodatečnou montáž M2 šrouby, udělat plošky pro šrouby

- Označení prvního pinu pro J1,J2 neodpovídá skutečnosti

/var/www/app/current/data/pages/pripravky/fpga/step4puf/start.txt · Poslední úprava: 2. 11. 2017 13:36:22 CET autor: bartimat